Yazar: Mehmet Ali Çavuşlu

Pasif Sonarlarda Teşhis İşlemleri için Deniz Taşıtlarının Akustik Sinyallerinin İncelenmesi

Bu çalışmada deniz taşıtlarının yaydığı gürültülerin özellikleri incelenmiştir. 4 farklı tip deniz taşıtının yaydığı gürültünün hıza bağımlı değişim grafikleri, pervane sayıları, kanat sayıları, makina ve silindir sayıları verilmiştir. Verilen bilgilerle, çalışmada tanımlanan deniz taşıtlarının sabit hızla seyrederken tespit mesafesi ve sınıflandırılabilmesi için gerekli süreleri hesaplanmıştır.

Deniz İçi Basınç Ölçümlerinde Dalga Basıncı Etkisi

Deniz içi basınç ölçümleri, deniz durumunu takip etme, derinlik ölçme, deniz taşıtlarını tanımlama, konumlama ve izleme gibi çeşitli amaçlarla kullanılmaktadır. Deniz durumuna bağlı olarak dalgalar önemli miktarda basınç yaratarak basınç ölçer üzerinde etkili olmaktadırlar. Basınç algılayıcıları, devrelerini ve sinyal işleme yöntemlerini en uygun biçimde tasarlamak ve deniz ortamını gerçekci modelleyen benzetim ortamı oluşturmak amacıyla, bu çalışmada, dalgaların deniz içinde oluşturduğu basınç etkileri incelenmiştir.

Gemi Hidrodinamik Basıncının Pratik Modellenmesi

Gemilerin hareketinden kaynaklanan hidrodinamik basınç alanlarının hesaplanması gemi geometrisinin ayrıntılı bilinmesini ve genellikle nümerik analiz yapılmasını gerektirir. Bazı uygulamalarda deniz içinde yapılan gemi basıncı ölçümleri, var-yok tespiti için kullanılır. Böyle uygulamalarda basınç sensörlerini, devrelerini ve sinyal işleme yöntemlerini en iyi tasarlayabilmek için, basit gemi oran ve verilerinden geminin yaratacağı basıncın tahmin edilebilmesi gerekir. Bu çalışmada literatürde bulunan bir ampirik formulasyon tanıtılmakta ve bu formulasyonlardan hareketle gemi hidrodinamik basıncının bazı özellikleri analiz edilmektedir

Deniz Platformlarının ve Sualtı Ortamının Akustik Sinyallerin Benzetimi

Bu çalışmada deniz ortamı ve taşıtlarının sahip olduğu akustik sinyal karakteristiklerini inceleyebilmek ve deniz taşıtlarının tespit ve teşhisi için algoritmalar geliştirilmesinde kullanılmak üzere bir benzetim ortamı oluşturulmuştur. Benzetimlerde, ortam gürültüsü Gauss dağılımlı ve durağan olmayan kabul edilmiştir. Deniz taşıtlarından yayınlanan akustik sinyaller makina, pervane vb elemanların yaratmış olduğu gürültülerdir. Bu gürültüler algılayıcı hidrofonda platformların hareketinden kaynaklanan dopler etkisi ve ortam şartlarındaki değişimlerden dolayı bozulmuş olarak algılanırlar. Bu yüzden deniz platformlarının yaydığı sinyaller, istatistikleri zamanla değişen rastlantısal süreçler olarak benzetimi yapılmıştır. Benzetim ortamı kullanıcı ara yüzü ile desteklenmiştir.

Ayrık Dalgacık Dönüşümü ve Ters Ayrık Dalgacık Dönüşümünün FPGA Tabanlı Donanımsal Gerçeklenmesi

Bu bildiride, Ayrık Dalgacık Dönüsümü ve Ters Ayrık Dalgacık Dönüsümlerinin FPGA tabanlı donanımsal gerçeklenmesi anlatılmaktadır. ADD ve TADD algoritmaları, Altera Cyclone-II FPGA’sı üzerinde donanımsal gerçeklenmistir. Satır ve sütun filtreleme islemleri level-bylevel mimarisinde olduğu gibi sırası ile uygulanmaktadır. Fakat verilerin okunma/yazma islemleri için adresleme, uygulanacak filtrenin türüne göre kontrol edilerek ADD ve TADD’nin tek filtre kullanılarak gerçeklenmesi sağlanmıstır. Bu tür kullanım hem okuma/yazma islemlerinde zaman kaybında hem de donanım alanı maliyetinde avantaj sağlamaktadır. Bu yaklasım ile, ADD ve TADD algoritmalarının donanımsal gerçeklenmesi için sadece %2’lik alan gerekmektedir.

Gerçek Zamanlı Nesne Tanıma Uygulamaları için HOG Algoritmasının FPGA Tabanlı Gömülü Sistem Uyarlaması

HOG algoritması son yıllarda kompleks içerikli görüntülerde nesne tanıma işlevini yüksek başarım ile gerçekleştirebilen bir algoritma olarak kullanılmaktadır. Bu basit fakat etkin tanımlayıcının donanımsal gerçeklenmesi bir çok temel örüntü tanıma işlevinde kullanılabilirliği söz konusu olduğundan önemlidir. Bu çalışmada HOG algoritmasının, farklı geometrik şekilleri yüksek bir başarım ile tanıyabilen donanımsal uyarlaması FPGA üzerinde gerçekleştirilmiştir. İncelenen görüntü içerisinde geometrik şeklin yatay ve dikey kenar bulma algoritmaları kullanılarak gradyan büyüklük ve açıları hesaplanmıştır. Elde edilen sonuçlar histogram üretmek için kullanılmış ve bu histogramların her bir şekil için ayırt edici karakteristiğe sahip olduğu gözlemlenmiştir. Kural tabanlı bir sınıflandırıcı uyarlanarak gerçek zamanlı olarak nesne tanıma uygulamalarında kullanılabilecek bir gömülü sistem yaklaşımı başarı ile sunulmuştur.

Plaka Yeri Tespiti için Kenar Bulma, Bit Tabanlı Öznitelik Çıkartma ve YSA Sınıflandırıcısının FPGA Üzerine Uyarlanması

Görüntü işlem ve örüntü tanıma problemleri gibi yoğun işlem yükü gerektiren işlevlerin gerçek zamanlı olarak gömülü sistemler üzerinde uyarlanması yarı-ilekten teknolojilerinde meydana gelen son yıllardaki gelişmeler ile mümkün olabilmiştir. Bu çalışmada plaka yeri tespit problemi için gömülü sistem alt birimlerinin parelel işlem yeteneğine sahip Alan Programlanabilir Kapı Dizisi (FPGA) üzerine uyarlanması gerçekleştirilmiştir. Geliştirilen altbirimler görüntü işlem ve örüntü tanıma uygulamalarında yoğun olarak kullanılmakta olan görüntü işlem ve sınıflandırıcı altbirimleridir. Bu altbirimler kenar bulma, istatistiksel bit-tabanlı öznitelik çıkarma ve yapay sinir ağı kullanılarak bir resim üzerinde plaka yerinin belirlenmesi işlevlerini başarı ile gerçekleştirmektedir. YSA’nın FPGA ile gerçeklenmesinde sabit noktalı sayı ve kayan noktalı sayı formatlarında ve farklı bit uzunluklarında işlem yapabilen 12 çarpma, 14 toplama ve 2 bölme modülü kullanıldı. Resim üzerinde ilk olarak Sobel süzgeci ile kenar bulma işlemi uygulandı. Elde edilen işlenmiş imge bit tabanlı öznitelik çıkartma amacı ile işlenerek elde edilen öznitelikler YSA giriş olarak sunuldu. YSA eğitiminde toplam 498 örnek kullanılmıştır. Bu örneklerin yarısı plaka içeren pozitif örnek diğer yarısı da plaka içermeyen negatif örnek olacak şekilde ayarlanmıştır. YSA donanım üzerinde gerçeklenmesinde paralel bir yapı kullanılmıştır. Ayrıca farklı sayı formatlarında yapılan uygulamalar sabit nokta sayı formatında işlem yapılması durumunda FPGA kaynaklarının kullanımında çok ciddi bir kazanım elde edilir iken, YSA sınıflandırıcısının eğitim başarımında ihmal edilebilecek oranda bir bozulma oluştuğunu göstermektedir. Yapılacak sunumda bilgisayar üzerinden FPGA’ya gönderilen imgeler yukarıdaki işlem aşamalarından geçirilerek donanım üzerinde plaka yeri bulma uygulaması gerçekleştirilecektir.

Yapay Sinir Ağı Eğitiminin IEEE 754 Kayan Noktalı Sayı Formatı ile Fpga Tabanlı Gerçeklenmesi

Bu bildiride, ileri beslemeli iki katmanlı bir Yapay Sinir Ağı(YSA)’nın geriye yayılım ile eğitiminin FPGA (Field Programmable Gate Array) üzerinde gerçeklenmesi ÖZEL-VEYA problemi baz alınarak anlatılmıştır. Çalışmada, YSA eğitim işlemlerinin (Çok Katmanlı Alıgılayıcı(ÇKA) ve Geriye Yayılım(GY)) FPGA üzerinde paralel gerçeklenmesi özellikle sağlanmıştır. Eğitimin gerçeklenmesinde Xilinx FPGA ailesine ait 2vp30fg676-7 yongası kullanılmıştır. Çalışma sonucunda az yer kaplayan ve çıkışta elde edilen hata değerinin önemsenmeyecek kadar küçük olduğu bir eğitim gerçeklenmiştir.

ÇKA Tipi Yapay Sinir Aği Kullanılarak Plaka Yeri Tespitinin FPGA’da Donanımsal Gerçeklenmesi

Görüntü islem ve örüntü tanıma problemleri gibi yoğun islem yükü gerektiren islevlerin gerçek zamanlı olarak gömülü sistemler üzerinde uyarlanması yarı-ilekten teknolojilerinde meydana gelen son yıllardaki gelismeler ile mümkün olabilmistir. Bu çalısmada plaka yeri tespit problemi için gömülü sistem alt birimlerinin parelel islem yeteneğine sahip Alan Programlanabilir Kapı Dizisi (FPGA) üzerine uyarlanması gerçeklestirilmistir. Gelistirilen altbirimler görüntü islem ve örüntü tanıma uygulamalarında yoğun olarak kullanılmakta olan görüntü islem ve sınıflandırıcı altbirimleridir. Bu altbirimler kenar bulma, istatistiksel bit-tabanlı öznitelik çıkarma ve yapay sinir ağı kullanılarak bir resim üzerinde plaka yerinin belirlenmesi islevlerini basarı ile gerçeklestirmektedir.

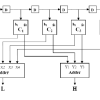

Hızlı Fourier Ve Ters Hızlı Fourier Dönüşümlerinin FPGA’da Donanımsal Olarak Gerçeklenmesi

Bu bildiride, HFD ve THFD algoritmalarının FPGA kiti üzerinde gerçeklenmesi anlatılmaktadır. Bu çalışmada FPGA kullanılmasının nedeni, FPGA’in tekrar düzenlenebilir mantık bloklarından oluşuyor olması ve aynı zamanda paralel veri işleme özelliğine sahip olmasıdır. Uygulamalar, Xilinx firmasına ait Virtex2P xc2vp30fg676-7 FPGA kiti üzerinde geliştirilmiştir. Kodlar VHDL dilinde yazılmıştır. HFD ve THFD algoritmalarının gerçeklenmesi için sırasıyla 60 ve 72 saat darbesi zaman gerekmektedir. Çalışmada, 100 MHz’lik osilator frekansına sahip FPGA ile gerçeklenme süreleri 0.6 µs ve 0.72 µs’lik işlem zamanlarına denk gelmektedir.