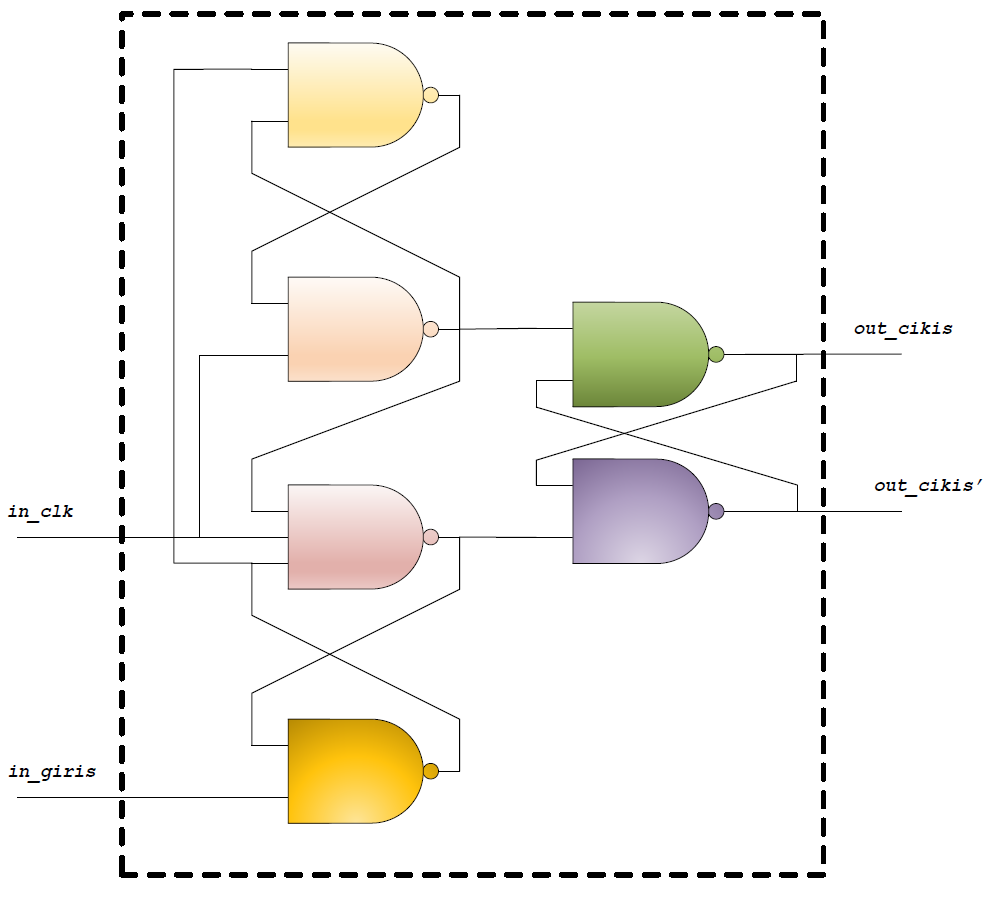

Yükselen kenar tetiklemeli D iki durumlusunda, saat darbesinin yükselen kenarına bağlı olarak çıkış değeri güncelleme işlemi yapılmaktadır. Yükselen kenar tetiklemeli D iki durumlusuna ait doğruluk tablosu Tablo 1’de verilmiştir. Tablo 1’dende görüleceği üzere saat darbesin yükselen kenarındain_giris giriş portunun değeri out_cikisçıkış portuna ve in_giris giriş portunun değerinin değili ise out_cikis’ çıkış portuna atanmaktadır. Saat darbesinin yükselen kenarı mevcut olmadığı durumlarda ise giriş değeri ne olursa olsun çıkış değerleri eski değerlerini korumaktadır. Şekil 1’de ise Yükselen kenar tetiklemeli D iki durumlusuna ait mantık devresi verilmiştir.

| Saat Darbesi | in_giris | out_cikis(+) | out_cikis'(+) |

| Çıkan kenar | 0 | 0 | 1 |

| Çıkan kenar | 1 | 1 | 0 |

| Çıkan kenar yok | X | out_cikis | out_cikis’ |

Şekil 9‑3 Yükselen kenar tetiklemeli D iki durumlusu mantık devresi

Örnek 1: Aşağıda yükselen kenar tetiklemeli D iki durumlu mantık devresinin gerçekleştirildiği d_mandali.vhd VHDL kodu verilmiştir. 1. ve 2. satırlarda tasarımda kullanılacak olan kütüphane bildirimleri yapılmaktadır. Tablo 1 ve Şekil 1’den de görülceği üzere d_mandali varlığımız iki giriş ve iki çıkış portuna sahiptir. Port tanımlamaya ilişkin bildirimler 5-10 satırları arasında yapılmaktadır. Port tanımalamaları std_logic veri tipinde yapıldığından dolayı 1. ve 2. satırlarda gerekli kütüphane bildirimleri yapılmaktadır.

15. satırda std_logic veri tipinde r_cikis sinyali tanımlanmaktadır. 19. satırda tanımlanan söz dizimi ile process’in in_clk ve in_giris giriş port değerlerinde meydana gelen değişiklikler ile aktif olacağı belirtilmektedir. 22. satırda tanımlı koşul ifadesinin sağlanması yani in_clk giriş portunda yükselen kenarının meydana gelmesi durumunda in_giris giriş port değeri r_cikis sinyaline atanmaktadır. Aksi durumlarda ise r_cikis sinyali bir önceki değerini korumaktadır. 28. satırda out_cikis çıkış portuna r_cikis sinyalinin değeri atanırken, 29. satırda ise out_cikis_degil çıkış portuna r_cikis sinyalinin değerinin değili atanmaktadır.

Eğer tasarım düşen kenar olarak tasarlanmak istenirse 22. satırdaki in_clk = ‘1’ koşulu in_clk = ‘0’ şeklinde değiştirilerek kullanılabilir.

library IEEE; use IEEE.STD_LOGIC_1164.all; entity d_mandali is port ( in_clk : in std_logic; in_giris : in std_logic; out_cikis : out std_logic; out_cikis_degil : out std_logic ); end d_mandali; architecture Behavioral of d_mandali is signal r_cikis : std_logic := '0'; begin process(in_clk, in_giris) begin if in_clk'event and in_clk = '1' then r_cikis <= in_giris; end if; end process; out_cikis <= r_cikis; out_cikis_degil <= (not r_cikis); end Behavioral;

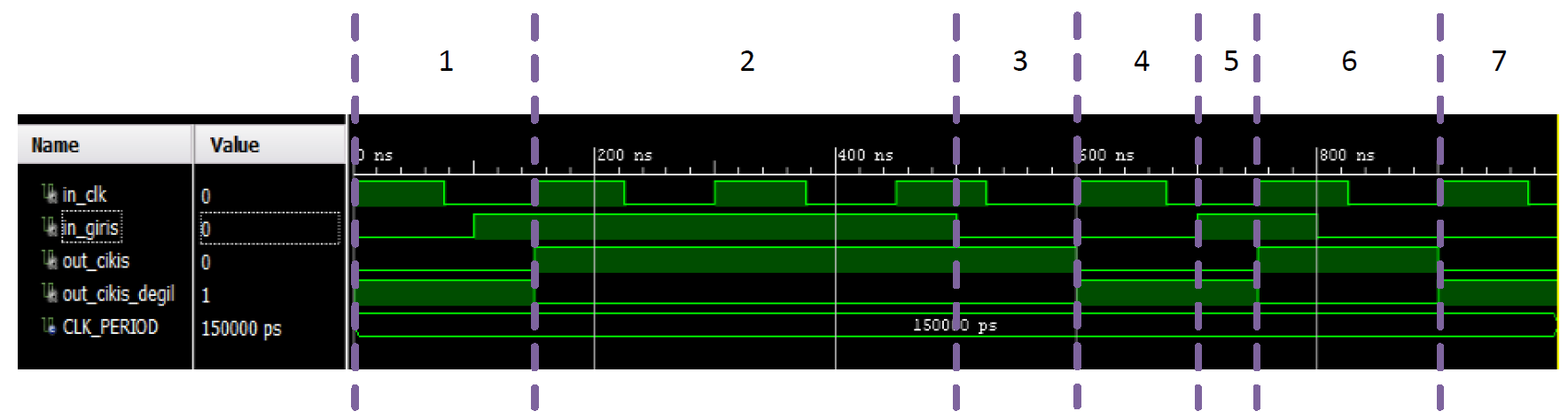

Aşağıda ise d_mandali varlığının benzetim yapılabilmesi için tb_d_mandali.vhd sınama kodu (test bench) verilmiştir ve benzetim çıktısı Şekil 2’de gösterilmiştir. Şekil 2’de gösterilen benzetim sonucunda:

1. adım: in_clk giriş portunda yükselen kenar meydana gelmesi ile birlikte in_giris giriş portu değeri r_cikis sinyaline atanmaktadır ve r_cikis sinyalinin değeri ‘0’ olmaktadır. r_cikis sinyalinin değerinin ‘0’ olması ile out_cikis çıkış portu değerine ‘0’, out_cikis_degil çıkış portu değerine ise ‘1’ atanmaktadır. 1. adım içerisinde in_giris giriş portu ‘1’ değerini almakta ve process aktif olmaktadır. Fakat 22. satırda tanımlanan in_clk giriş portunda saat darbesi yükselen kenarının meydana gelip gelmediğini kontrol eden koşul ifadesi gerçeklenmediğinden dolayı çıkış portlarının değerleri değişmemiştir.

2. adım: in_clk giriş portunda yükselen kenar meydana gelmesi ile birlikte in_giris giriş portu değeri r_cikis sinyaline atanmaktadır ve r_cikis sinyalinin değeri ‘1’ olmaktadır. r_cikis sinyalinin değerinin ‘1’ olması ile out_cikis çıkış portu değerine ‘1’, out_cikis_degil çıkış portu değerine ise ‘0’ atanmaktadır

3. adım: in_giris giriş portu ‘0’ değerini almakta ve process aktif olmaktadır. Fakat 22. satırda tanımlanan in_clk giriş portunda saat darbesi yükselen kenarının meydana gelip gelmediğini kontrol eden koşul ifadesi gerçeklenmediğinden dolayı çıkış portlarının değerleri değişmemiştir.

4. adım:in_clk giriş portunda yükselen kenar meydana gelmesi ile birlikte in_giris giriş portu değeri r_cikis sinyaline atanmaktadır ve r_cikis sinyalinin değeri‘0’ olmaktadır. r_cikis sinyalinin değerinin ‘0’ olması ile out_cikis çıkış portu değerine ‘0’, out_cikis_degil çıkış portu değerine ise ‘1’ atanmaktadır

5. adım : in_giris giriş portu ‘1’ değerini almakta ve process aktif olmaktadır. Fakat 22. satırda tanımlanan in_clk giriş portunda saat darbesi yükselen kenarının meydana gelip gelmediğini kontrol eden koşul ifadesi gerçeklenmediğinden dolayı çıkış portlarının değerleri değişmemiştir.

6. adım :in_clk giriş portunda yükselen kenar meydana gelmesi ile birlikte in_giris giriş portu değeri r_cikis sinyaline atanmaktadır ve r_cikis sinyalinin değeri ‘1’ olmaktadır. r_cikis sinyalinin değerinin ‘1’ olması ile out_cikis çıkış portu değerine ‘1’, out_cikis_degil çıkış portu değerine ise ‘0’ atanmaktadır. 6. adım içerisinde in_giris giriş portu ‘0’ değerini almakta ve process aktif olmaktadır. Fakat 22. satırda tanımlanan in_clk giriş portunda saat darbesi yükselen kenarının meydana gelip gelmediğini kontrol eden koşul ifadesi gerçeklenmediğinden dolayı çıkış portlarının değerleri değişmemiştir.

7. adım :in_clk giriş portunda yükselen kenar meydana gelmesi ile birlikte in_giris giriş portu değeri r_cikis sinyaline atanmaktadır ve r_cikis sinyalinin değeri ‘0’ olmaktadır. r_cikis sinyalinin değerinin ‘0’ olması ile out_cikis çıkış portu değerine ‘0’, out_cikis_degil çıkış portu değerine ise ‘1’ atanmaktadır.

Şekil 2 d_mandali varlığı benzetim çıktısı

tb_d_mandali.vhd VHDL kodun amacı d_mandali varlığının benzetiminin yapmak olduğundan dolayı tb_d_mandali varlığına ait bir port tanımlaması yapılmamıştır. tb_d_mandali.vhd VHDL kodu sentezlenemez sadece benzetim için kullanılabilmektedir. 18. satırda saat darbesinin periyodunun belirlendiği sabit tanımlaması yapılmıştır. Tanımlamada saat darbesi periyodu 150 ns olarak belirlenmiştir. Test kodlarının oluşturulması amacı ile kullanılacak olan sinyallerin tanımlama işlemleri 19-22. satırlarda yapılmıştır.

26-33. satırlar arasında tanımlanan process ile in_clk saat darbesi sinyalinin davranışı tanımlanmaktadır. 30. satırda in_clk sinyaline ‘1’ değeri atanmakta ve 31. satırda tanımlanan ifade ile saat darbesi periyodunun yarısı kadar beklenmektedir. 32. satırda in_clk sinyaline ‘0’ değeri atanmakta ve 33. satırda tanımlanan ifade ile saat darbesi periyodunun yarısı kadar beklenmektedir. Bu şekilde %50 doluluk oranında saat darbesi elde edilmiştir.

35-42. satırları arasında tanımlanan process içerisinde in_giris sinyalinin davranışı tanımlanmaktadır. 37. satırda tanımlanan ifade ile in_giris sinyalinin 0-100 ns aralığında alacağı değerin ‘0’ olacağı belirtilmektedir. 38. satırda tanımlanan ifade ile in_giris sinyalinin 100-500 ns aralığında alacağı değerin ‘1’ olacağı belirtilmektedir. 39. satırda tanımlanan ifade ile in_giris sinyalinin 500-700 ns aralığında alacağı değerin ‘0’ olacağı belirtilmektedir. 40. satırda tanımlanan ifade ile in_giris sinyalinin 700-800 ns aralığında alacağı değerin ‘1’ olacağı belirtilmektedir. 41. satırda tanımlanan ifade ile in_giris sinyalinin 800-1000 ns aralığında alacağı değerin ‘0’ olacağı belirtilmektedir.

d_mandali varlığının tb_d_mandali varlığında alt devre olarak kullanılabilmesi için gerekli component tanımlama işlemleri 9-16. satırlar arasında yapılmıştır. 44-50. satırlar arasında ise d_mandali alt devresine ilişkin bağlantılar yapılmaktadır.

library IEEE; use IEEE.STD_LOGIC_1164.all; entity tb_d_mandali is end tb_d_mandali; architecture Behavioral of tb_d_mandali is component d_mandali Port ( in_clk : in std_logic; in_giris : in std_logic; out_cikis : out std_logic; out_cikis_degil : out std_logic ); end component; constant CLK_PERIOD : time := 150 ns; signal in_clk : std_logic := '0'; signal in_giris : std_logic := '0'; signal out_cikis : std_logic := '0'; signal out_cikis_degil : std_logic := '0'; begin process begin in_clk <= '1'; wait for CLK_PERIOD / 2; in_clk <= '0'; wait for CLK_PERIOD / 2; end process; process begin in_giris <= '0'; wait for 100 ns; in_giris <= '1'; wait for 400 ns; in_giris <= '0'; wait for 200 ns; in_giris <= '1'; wait for 100 ns; in_giris <= '0'; wait for 200 ns; end process; d_mandali_map : d_mandali Port map ( in_clk => in_clk, in_giris => in_giris, out_cikis => out_cikis, out_cikis_degil => out_cikis_degil ); end Behavioral;