4 bitlik bir toplayıcı için art arda 4 adet tam toplayıcı devresinin birbirine bağlanması gerekmektedir. Eğer tasarlanan sistem 4 bitlik yerine artık 8 bitlik bir toplayıcı olarak kullanılacaksa bu sefer 8 adet tam toplayıcı devresinin birbirine bağlanması gerekmektedir. Bu sayı arttıkça kod içerisinde yapılacak değişikliklerin sayısı da artmaktadır (Şekil 1). Bu durumu kontrol altına alabilmek amacı ile VHDL dilinde parametrik tasarım yapılabilmesi için generic tanımlama mevcuttur.

generic tanımlaması yapılarak tasarlanan devre parametrik özelliğe sahip olmaktadır. Özellikle büyük tasarımlarda generic kullanımıyla yapılmak istenen değişiklikler kolaylıkla yapılabilmektedir.

generic olarak tanımlanan ifadeler yapılacak değişikliklerle tasarlanan tasarımın tamamı değiştirilmektedir. Bu nedenle kullanıcı tasarım içerisinde yapacağı değişiklikleri tek tek yapmak yerine generic ile daha kolay yapma imkânına sahip olmaktadır.

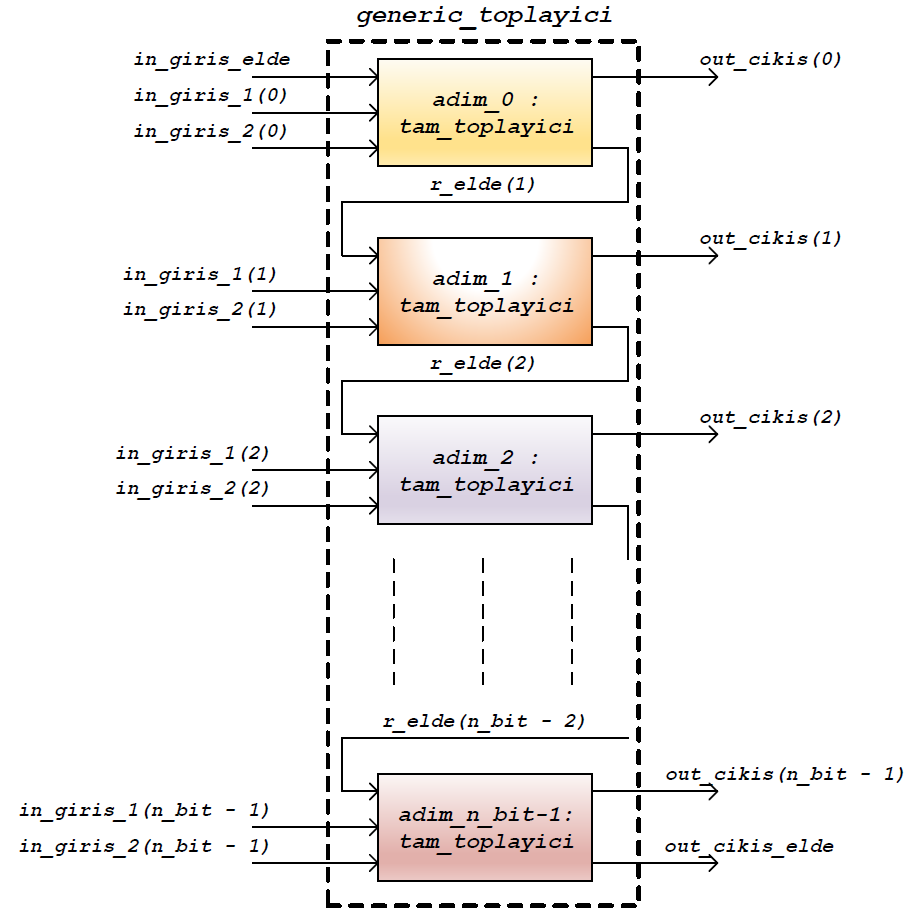

Örnek 1: Şekil 1’de verilen blok şemaya ait generic_toplayici.vhd VHDL kodu aşağıda verilmiştir. Kodda parametrik yapıda tam toplayıcı işlemi gerçekleştirilmiştir. Parametrik işlem kodda 5-7. satırlar arasında tanımlanan n_bit parametresi ile sağlanmaktadır.

generic_toplayici varlığımızın port tanımlama işlemleri 8-14. satırlar arasında yapılmaktadır. in_giris_elde portu in modunda std_logic tipindedir. in_giris_1 ve in_giris_2 portları in modunda n_bit bitlik std_logic_vector tipindedir. out_cikis portu out modunda n_bit bitlik std_logic_vector tipindedir. out_cikis_elde portu out modunda std_logic tipindedir.

Şekil 1 n bitlik tam toplayıcı devresinin alt devre kullanılarak gösterimi

6. satırda tanımlanan n_bit : integer := 8 söz dizimi ile tasarlanacak sistemimizde kullanılacak olan n_bit değişkeni 8 değerini alacaktır. n_bit değerini belirlenmesi ile birlikte generic_toplayici varlığımıza ait in_giris_1, in_giris_2 ve out_cikis portları 8 bit olacaktır.

Mimari içerisinde 35. satırda tanımlanan for n_i in 0 to n_bit – 1 generateifadesi ile döngü içerisinde tanımlanacak olan ifade ile oluşturulacak devreden n_bit adedinin birbirine bağlanacağı ifade edilmektedir. 36. satırda adim: tam_toplayici port mapifadesi ile n_bit adet tam toplayici devresinin bir biri ardına bağlanacağı anlaşılmaktadır.

Tasarımımızda toplayıcının bit uzunluğunu değiştirmek istediğimizde kod içersinde n_bit ve n_bit – 1 gördüğümüz yerlerdeki tüm değerleri ayrı ayrı değiştirmemiz gerekmektedir. Tasarlanın devrenin de büyüklüğü düşünüldüğü zaman yapılacak değişiklikler daha da karmaşık hale gelebilmektedir. Bu nedenle generic kullanımı ile tasarımda değişikliklerin kolayca yapılabildiği görülmektedir.

library IEEE; use IEEE.STD_LOGIC_1164.all; entity generic_toplayici is Generic( n_bit : integer := 8 ); Port( in_giris_elde : in std_logic; in_giris_1 : in std_logic_vector(n_bit - 1 downto 0); in_giris_2 : in std_logic_vector(n_bit - 1 downto 0); out_cikis : out std_logic_vector(n_bit - 1 downto 0); out_cikis_elde : out std_logic ); end generic_toplayici; architecture Behavioral of generic_toplayici is component tam_toplayici Port ( in_giris_elde : in std_logic; in_giris_1 : in std_logic; in_giris_2 : in std_logic; out_cikis : out std_logic; out_cikis_elde : out std_logic ); end component; signal r_elde : std_logic_vector(0 to n_bit) ; begin r_elde(0) <= in_giris_elde; for_kontrol: for n_i in 0 to n_bit - 1 generate adim: tam_toplayici port map ( in_giris_elde => r_elde(n_i), in_giris_1 => in_giris_1(n_i), in_giris_2 => in_giris_2(n_i), out_cikis => out_cikis(n_i), out_cikis_elde => r_elde(n_i + 1) ); end generate for_kontrol; out_cikis_elde <= r_elde(n_bit); end Behavioral;

Aşağıda verilen tb_toplayici.vhd VHDL kodunda farklı bit uzunluklarında generic_toplayici alt devreleri oluşturulmaktadır. generic_toplayici_4_bit etiketli alt devre de görüleceği üzere generic içerisinde n_bit => 4 atama işlemi yapılmıştır. Bu nedenle bu alt devre 4 bitlik olacaktır. generic_toplayici_8_bit etiketli alt devre de ise generic atama işlemi yapılmamıştır. Bu durumlarda ise component içerisinde tanımlanan n_bit değeri varsayılan değer olarak atanmaktadır. Bu tasarım için 8 bitlik bir toplayıcı oluşturacaktır. port map içerisinde çıkış değerleri kullanılmayacak ise uygulamada görüldüğü gibi open ile açık hale getirilebilmektedir.

library IEEE; use IEEE.STD_LOGIC_1164.all; entity tb_toplayici is end tb_toplayici; architecture Behavioral of tb_toplayici is component generic_toplayici Generic( n_bit : integer := 8 ); Port ( in_giris_elde : in std_logic; in_giris_1 : in std_logic_vector(n_bit - 1 downto 0); in_giris_2 : in std_logic_vector(n_bit - 1 downto 0); out_cikis : out std_logic_vector(n_bit - 1 downto 0); out_cikis_elde : out std_logic ); end component; signal in_giris4_1 : std_logic_vector(3 downto 0) := X"2"; signal in_giris4_2 : std_logic_vector(3 downto 0) := X"1"; signal out_cikis4 : std_logic_vector(3 downto 0); signal out_cikis_elde4 : std_logic; signal in_giris8_1 : std_logic_vector(7 downto 0) := X"12"; signal in_giris8_2 : std_logic_vector(7 downto 0) := X"22"; signal out_cikis8 : std_logic_vector(7 downto 0); begin generic_toplayici_4_bit : generic_toplayici Generic map( n_bit => 4 ) Port map ( in_giris_elde => '0', in_giris_1 => in_giris4_1, in_giris_2 => in_giris4_2, out_cikis => out_cikis4, out_cikis_elde => out_cikis_elde4 ); generic_toplayici_8_bit : generic_toplayici Port map ( in_giris_elde => '0', in_giris_1 => in_giris8_1, in_giris_2 => in_giris8_2, out_cikis => out_cikis8, out_cikis_elde => open ); end Behavioral;